### Digital Computer Laboratory Massachusetts Institute of Technology Cambridge, Massachusetts

SUBJECT: DESIGN OF A DIGITAL COMPUTER BY BOOLEAN ALGEBRA

To:

N. H. Taylor

From:

R. C. Jeffrey, I. S. Reed

Date:

May 20, 1952

Abstract: The techniques described in E-458-1 are illustrated in a reallife situation: the design of a 4-order machine employing an unusual method of central control. For definiteness the memory size is taken to be 8 words, but no logical complexity is added

when this is increased to a realistic figure.

#### 1.0 SPECIFICATIONS FOR THE MACHINE: NOMENCLATURE

1.1 Words: 5 bits, interpreted as in WWI, with negative numbers represented in nine complement form.

Interpreted as a number: Sg(X)

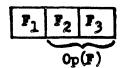

$\frac{\left[\begin{array}{ccccc} x_0 & x_1 & x_2 & x_3 & x_4 \\ \hline 0 & (x) & Ad(x) \end{array}\right]}{\left[\begin{array}{cccc} x_0 & x_1 & x_2 & x_3 & x_4 \\ \hline \end{array}\right]}$ Interpreted as an instruction:

1.2 Memory: 8 words, stored in flip-flops. An actual memory would use some other device, such as iron cores; but the analysis for the flipflop case can easily be applied to whatever device is actually used.

#### 1.3 Registers

Arithmetic Element

| A-Register                                             | B-Register                                            |  |

|--------------------------------------------------------|-------------------------------------------------------|--|

| Receives number from storage                           | Accumulator<br>(A subtracter)                         |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |

### C-Register

Holds address of next memory register to be used.

|   | C <sub>2</sub> | C <sub>3</sub> | CA |

|---|----------------|----------------|----|

| į | ~              | 2              | 4  |

### F-Register

Operation counter; central control.

Start Flip-Flop

G

#### Memory

"M(C)" denotes the address in memory corresponding to the number in the C-register. Thus if the C-register holds 101, M(C) is

### 1.4 Operations'

The decisions as to word length, number of registers, etc., summarized above come under the heading of machine planning, and were arrived at by cut-and-try. The last and most delicate part of the planning concerns the operation of central control.

| Cede No. | Name                      | Description                                                                                                                                                                          |

|----------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00xyz    | Halt .                    | The machine stops, i.e., all flip-flops remain in the states they were in when the operation was executed, until the start button is depressed, at which time program timing begins. |

| Olxyz    | Conditional<br>Subprogram | If the sign digit of the B-register is 1, take next instruction from memory location xyz.  If the sign of the B-register is 0, take mext instruction in sequence.                    |

| 10xyz    | Subtract                  | Take number from memory location xyz<br>and put it in the A-register; subtract<br>it from the contents of the B-register<br>and leave the result in B.                               |

| llxyz    | Shift right               | Shift the contents of the B-register right, depositing the original contents of B in M(C).                                                                                           |

#### 2.0 TIMING DIAGRAM

# 2.1 Notation

The above four operations are to be performed as sequences of commands to perform the elementary independent functions of which the machine is capable. In order to describe these functions we adopt a compact terminology:

- M(C): The memory location whose number is stored in C.

- X: The X register.

- (I): The contents of the I register.

- (I) → I: The contents of register I at time t appear im register I at time t + €.

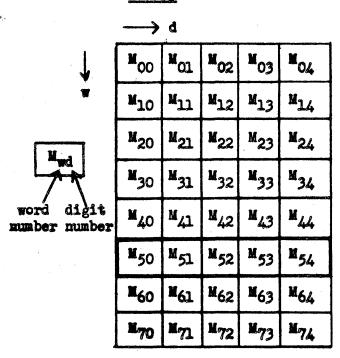

Then it is possible to have "simultaneous" interchanges:

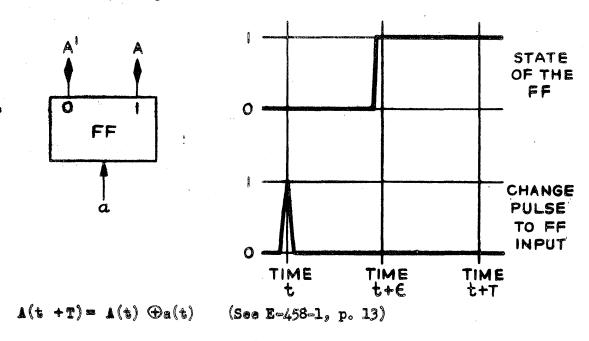

"(X)  $\Rightarrow$  Y and (Y)  $\Rightarrow$  X" means that the contents of X at t appear in Y at t  $+ \in$ , and that the contents of Y at t appear in X at t  $+ \in$ . This can be implemented by delay elements (which we shall henceforth assume to be built into the FF's):

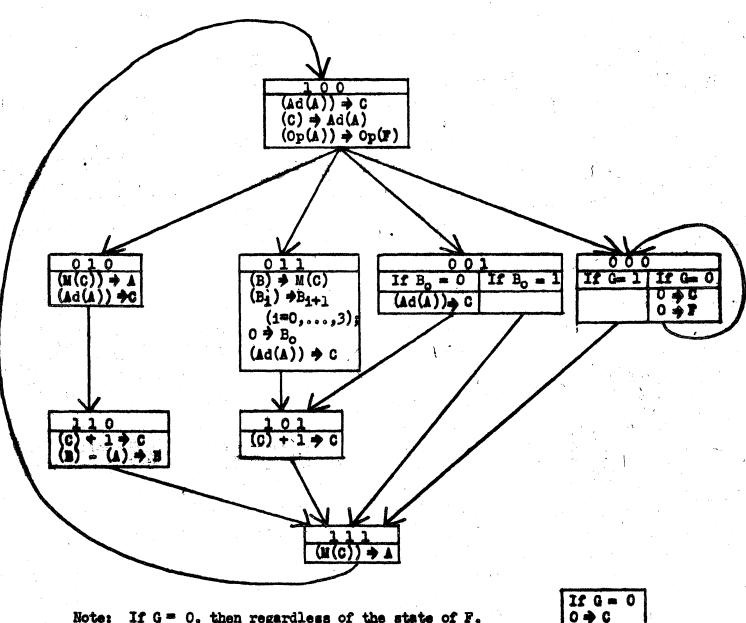

We now draw a <u>flow diagram</u> for central control (next page). The numbers at the tops of the boxes will represent states of the F-counter, and the notations inside the boxes represent the commands which are performed by the first time pulse during which the F-counter is in the indicated state.

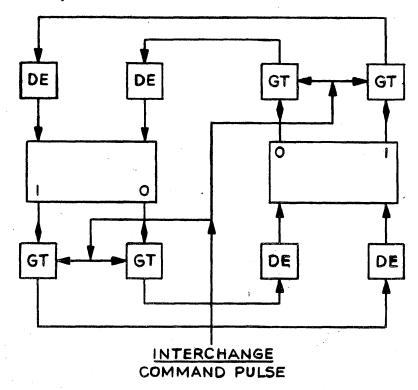

For example, in the upper left corner on page 5

means that when the F-register is in the configuration  $F_1 = 0$ ,  $F_2 = 1$ ,  $F_3 = 0$  the commands read out of memory location (C) into the A-register and read the last three (address) digits of the A-register into the C-register are performed and the F-counter changes to the configuration 110 (i.e.,  $F_1$  is complemented). This change in (F) is strictly speaking a command, but is indicated by the arrow between the boxes instead of by a third notation inside the upper box.

For further explanation of the flow diagram, see page 6.

# 2.2 Flow Diagram

(The numbering of the boxes should be thought of as arbitrary, for the present. See Section 4.0 below.)

Note: If G = 0, then <u>regardless</u> of the state of F, both the F and C registers are cleared:

| T | I | ľ | G   | - | 0 | ٦ |

|---|---|---|-----|---|---|---|

| ۱ | 0 | 4 | )   | C |   |   |

| ۱ | 0 |   | ١ ( | 7 |   | 1 |

Program timing occurs at 111 and 100. Note that the C-register is used both as a storage selection register and a program counter: in 110 and 101 we add 1 to (C) . Each of the four paths after 100 corresponds to an operation:

010 begins the operation timing for <u>subtract</u> (10xyz) 011 begins the operation timing for <u>shift</u> (11xyz) 001 begins the operation timing for <u>cp</u> (01xyz) 000 begins the operation timing for <u>halt</u> (00xyz)

The four way decision is determined by the result of the command  $(Op(A)) \not\ni Op(F)$ , which reads  $(A_{\odot})$  into  $F_2$  and  $(A_1)$  into  $F_3$ . At the beginning of operation timing for operation number v w the F-register will be in configuration O v w, since previously we had  $(A_0)$  =v and  $(A_1)$  =v for Op(A). It is also necessary to arrange that  $F_1$  be complemented when the F-counter leaves configuration 100.

The reader should now werify that the sequences of commands specified in the flow diagram really do add up to the four operations listed above. The logical details are discussed in section 3.

# 3.0 DESIGN OF THE MACHINE: INPUT EQUATIONS

### 3.1 Design of the F-Register

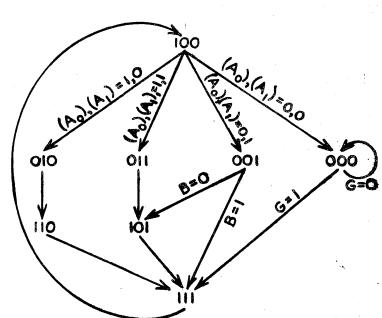

Apparently the F-register is to be a 3 stage binary counter with the following cycle:

We name the configurations of the F-register:

$$P_0 = P_1 P_2 P_3$$

... 000

$P_1 = P_1 P_2 P_3$  ... 001

$P_2 = P_1 P_2 P_3$  ... 010

$P_3 = P_1 P_2 P_3$  ... 100

$P_4 = P_1 P_2 P_3$  ... 101

$P_6 = P_1 P_2 P_3$  ... 110

$P_7 = P_1 P_2 P_3$  ... 111

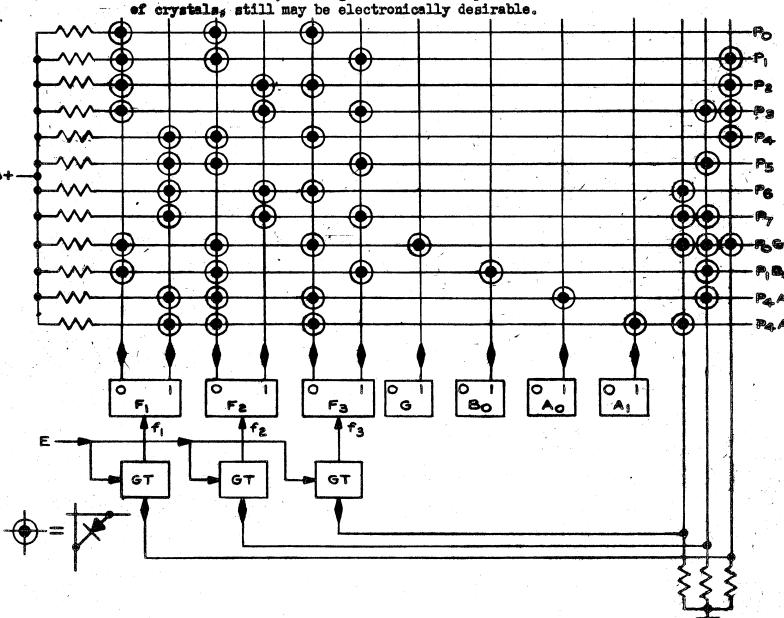

The block diagram on page 9 shows how voltages corresponding to the P<sub>1</sub> are generated.

In the table above, the binary representation of the subscript of P indicates, by the distribution of zeros, the location of the primes in the product of the F's.

Now the successive states of the counter are determined by information external to the counter, as well as from the configuration of the counter itself. For example, from P<sub>3</sub> the counter must go to P<sub>5</sub>, but from P<sub>1</sub> it may go to P<sub>5</sub> or to P<sub>7</sub>. It is necessary to indicate the basis on which this selection is made; this is done in the cases where a choice is necessary.

Assume that the FF's used have one input, such that if that input is pulsed at time t, the FF is complemented at time  $t+\varepsilon$ ,  $\varepsilon$  being a delay less than T, the period of the clock.

Now to design the F-counter it is sufficient to write three equations, one for each stage, specifying when the change inputs are to be pulsed. We shall work through the lattice on page 6 (or page 5) level by level for each input. The equations we are about to build up are illustrated by a block diagram on page 9.

For the first digit  $(F_1)$  we see that in going from  $P_4$  (=100) on the first level to the second,  $F_1$  is to be complemented regardless of which of the four configurations on the second level is selected:

$$f_1 = (P_{\perp} + \dots )E$$

Here E denotes the clock pulse: the changes are to occur at each clock pulse, so that an operation will require at most 4 clock pulses for its completion.

To get the second term: if P2 (=010) is the second level configuration selected, the first digit must change again to get the configuration 110:

$$\mathbf{f}_1 = (\mathbf{P}_4 + \mathbf{P}_2 + \dots)\mathbf{E}$$

Ditto in case Oll was the second level configuration selected: to get from Oll to 101, F, must be complemented:

$$f_1 = (P_4 + P_2 + P_3 + \dots)E$$

Similarly, whichever value B<sub>0</sub> may have, the F-counter will go from the configuration 001 to a configuration (101 or 111) in which the first digit is changed:

$$f_1 = (P_4 + P_2 + P_3 + P_1 + \dots)E$$

Finally, the counter goes from 000 to 111 in case G=1. Thus  $F_1$  will change in case  $P_0G$ . (" $P_0G$ " means  $P_0=1$  and G=1.)

$$f_1 = (P_4 + P_2 + P_3 + P_1 + P_0G)E$$

Since F, does not change in going from 111 to 100, the above formula represents all the conditions under which F, must be complemented.

Similarly, for  $\mathbf{F}_2$  we have

$$f_2 = (A_0P_4 + P_3 + B_0P_1 + QP_0 + P_5 + P_7)B$$

where the first term derives from the fact that in the two cases where  $A_0 = 1$   $O_p(A) = 10$  and  $O_p(A) = 11$  the second digit of "100" must be changed, but in the other two cases (when "100" goes to "001" or to "000") this is not necessary. Finally

$$f_3 = (A_1P_4 + GP_0 + P_6 + P_7)E$$

It remains to implement the condition that if G=0, 0=F. Note that if a halt is programmed, the F-counter steps from 100 to 000 and in so doing clears G. But as will be seen in Section 3.35 below, G can also be cleared by a pushbutton. We wish to provide that if G=0 from any cause, the F-counter will assume the configuration 000 on the next time pulse.

This is most easily accomplished by writing three equations for the <u>clear</u> inputs to the F flip-flops:

$$o^{f_i} = G^{i}E$$

$i = 1,2,3$

Now these equations may be realized immediately by a two-level diode matrix which, although it does not represent a minimization of number of creately, still may be electronically desirable.

Here we have indicated only those 3 outputs of the diode matrix which feed back into the F-register. Actually we require other outputs: command pulses to the rest of the machine. They will be considered below in connection with the FF registers which they centrol.

# 3.2 Digression on "Levels"

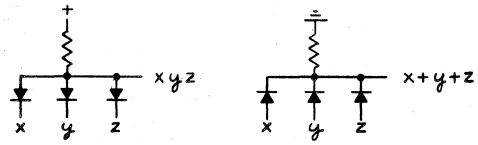

Note that the three equations for the F-register can be factored, resulting in a reduction in the number of gates and mixers required for the realization of central control. But this numerical reduction is at the expense of an increase in the number of <u>levels</u> of gating and mixing. We illustrate the meaning of "levels" by examples.

EXAMPLE

| No. of Levels | Equations        | Block Diagress  | One Electronie<br>Realization (Diede)              |

|---------------|------------------|-----------------|----------------------------------------------------|

| 1             | <b>x + y</b>     | x               | x+y<br>x <del>y</del> <del>y</del>                 |

|               | Xy               | x —□GT → xy     | ×                                                  |

|               | <b>z</b> (y + z) | x—DGT — x(y+z)  | x <del>                                     </del> |

|               | x † ys           | x               | x-94 - 19 - 12 - 14 - 21 - 21 - 21 - 21 - 21 - 21  |

|               |                  | x-bGT - x(y+mv) | x(y+uv)<br>x- <del>10+1</del>                      |

| 3             | x[7 + uv]        | y               | 4-14-14-1                                          |

Apparently in terms of the equations, the number of levels is the same as the <u>functional complexity</u> of the expression for the output. That is, x + y and xy are functions whose arguments are variables; x(y + z) and x + (yz) are functions (the first a product and the second a sum) in which one of the arguments is itself a function of variables.

Finally, x y + uv is a <u>product</u> one of whose factors is a <u>sum</u> one of whose terms is a <u>product</u>: " $\pi\{x, \sigma[y, \pi(u, v)]\}$ " in functional notation where  $\pi(a, b) = ab$  and  $\sigma(a, b) = a + b$ . Briefly, the number of levels in a Boolean function is identical with the number of <u>nestings</u> of parentheses within each other.

In terms of block diagrams, the number of levels in a device is determined by drawing lines from each input to the output; the largest number of gates and mixers through which such a line passes in the <u>level</u> of the system. Finally, the reason we are interested in levels is that if a function of level n is realized with diodes, n is the largest number of diodes through which any input current must pass in order to reach the output. In a high-level diode network considerable attention must be paid to the values of voltage and resistance associated with the diodes. Other difficulties arise with high-level vacuum tube and transistor networks. In all cases the difficulties simply require engineering attention: high-level networks are realizable.

One last comment: in such expressions as "xyz" and "x + y + z", the product and sum are regarded as functions of three variables:

$$\pi_3(x,y,z) = xyz$$

and  $\sigma_3(x,y,z) = x + y + z$

Electronically this corresponds to the use of three-input diode devices for mixing and gating:

and therefore three-input gates and mixers are first level networks. However, expressions like "x + (y + z)", which might be written in functional notation as  $\sqrt[6]{2}(x\sqrt[6]{2}y,z)$  have as their direct realizations two-level mixers like:

in which the longest current path passes through two diodes. The two sorts of mixers are logically equivalent, and the one-level type is used where possible.

To illustrate these points, let us factor the equations of the F-register:

$$f_{1} = P_{1} + P_{2} + P_{3} + P_{4} + P_{0}G \quad (Ignore the "E" for the present.)$$

$$= P_{1}^{\circ} P_{2}^{\circ} P_{3} + P_{1}^{\circ} P_{2}^{\circ} P_{3} + P_{1}^{\circ} P_{2}^{\circ} P_{3} + F_{1}^{\circ} P_{2}^{\circ} P_{3}^{\circ} P_{3}^{\circ} P_{2}^{\circ} P_{3}^{\circ} P_{$$

$$f_{2} = A_{0}P_{4} + P_{3} + B_{0}P_{1} + GP_{0} + P_{5} + P_{7}$$

$$= A_{0}F_{1}F_{2}^{\dagger}F_{3}^{\dagger} + F_{1}^{\dagger}F_{2}F_{3} + B_{0}F_{1}^{\dagger}F_{2}^{\dagger}F_{3} + GF_{1}^{\dagger}F_{2}^{\dagger}F_{3}^{\dagger} + F_{1}F_{2}^{\dagger}F_{3} + F_{1}F_{2}F_{3}$$

$$= F_{1}(A_{0}F_{2}^{\dagger}F_{3}^{\dagger} + F_{2}^{\dagger}F_{3} + F_{2}F_{3}^{\dagger}) + F_{1}^{\dagger}(F_{2}F_{3} + B_{0}F_{2}^{\dagger}F_{3} + GF_{2}^{\dagger}F_{3}^{\dagger})$$

$$= F_{1}(A_{0}F_{2}^{\dagger}F_{3}^{\dagger} + F_{3}^{\dagger}) + F_{1}^{\dagger}F_{3}(F_{2} + B_{0}F_{2}^{\dagger}) + GF_{2}^{\dagger}F_{3}^{\dagger}$$

$$= F_{1}(F_{3} + A_{0}F_{2}^{\dagger}) + F_{1}^{\dagger}F_{3}(F_{2} + B_{0}) + GF_{2}^{\dagger}F_{3}^{\dagger}$$

$$f_{2} = \{F_{1}(F_{3} + A_{0}F_{2}^{\dagger}) + F_{1}^{\dagger}F_{3}(F_{2} + B_{0}) + GF_{2}^{\dagger}F_{3}^{\dagger}\}E$$

$$f_{3} = A_{1}P_{4} + GP_{0} + P_{6} + P_{7}$$

$$= A_{1}F_{1}F_{2}^{\dagger}F_{3}^{\dagger} + GF_{1}^{\dagger}F_{2}^{\dagger}F_{3}^{\dagger} + F_{1}F_{2}F_{3}^{\dagger} + F_{1}F_{2}F_{3}^{\dagger}$$

$$= F_{1}(A_{1}F_{2}^{\dagger}F_{3}^{\dagger} + F_{2}F_{3}^{\dagger} + F_{2}F_{3}^{\dagger}) + GF_{1}^{\dagger}F_{2}^{\dagger}F_{3}^{\dagger}$$

$$= F_{1}(A_{1}F_{2}^{\dagger}F_{3}^{\dagger} + F_{2}^{\dagger}) + GF_{1}^{\dagger}F_{2}^{\dagger}F_{3}^{\dagger}$$

$$= F_{1}(A_{2}F_{3}^{\dagger}F_{3}^{\dagger} + F_{2}^{\dagger}) + GF_{1}^{\dagger}F_{2}^{\dagger}F_{3}^{\dagger}$$

$$f_{3} = F_{1}(F_{2} + A_{1}F_{3}^{\dagger}) + GF_{1}^{\dagger}F_{2}^{\dagger}F_{3}^{\dagger}$$

We have now reduced the total number of diodes (assuming a realization as a diode net) from 55 in the two-level matrix to 41 [10 for  $f_1$ , 19 for  $f_2$ , 12 for  $f_3$ : this can be determined directly from the equation by counting n diodes for each n input gate or mixer. E.g., for  $f_3$ ..... ignoring E.... we have a 2 input mixer (the plus in front of "G") of which the inputs are a 4 input gate and a 2 input gate of which the inputs are  $F_1$  and a 2 input mixer of which the inputs are  $F_2$  and a 2 input gate. Adding up the numbers of inputs underlined above gives the 12 diodes required for  $f_3$ .

We shall not draw the block diagrams for the factored equations. It would be very messy, and an engineer who understands the algebraic notation could design the network from the equations as easily as he could from the block diagrams (the equations have the added advantage of compactness: three rows of symbols, instead of a page crammed with boxes, lines and arrows).

#### 3.3 The Arithmetic Element

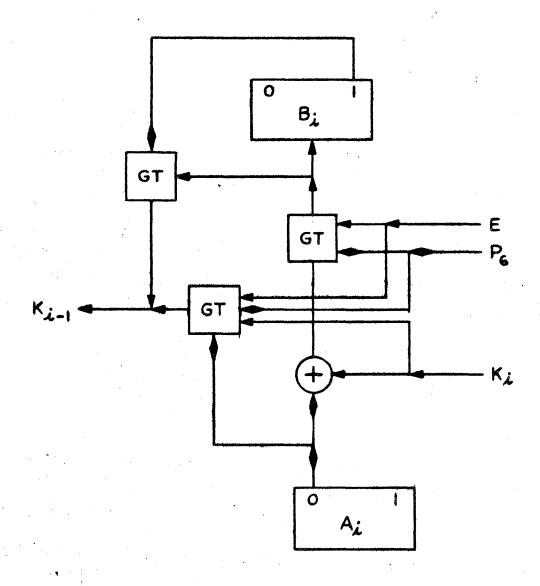

# 3.31 The Subtractor (See diagram on p. 26)

The most complicated single command the machine must execute is subtract  $(B) - (A) \Rightarrow B$ ; from the contents of the B-register, subtract the contents of the A-register and deposit the result back in B

Now representing the binary number stored in the A-register by  $^{1}A^{1}$ , and similarly for B, and denoting the nines complement (result of complementing each digit) of A by  $^{1}\overline{A}^{1}$ , we have

$$B = B_0 2^0 + B_1 2^{-1} + B_2 2^{-2} + B_3 2^{-3} + B_4 2^{-4}$$

$$A = A_0 2^0 + \dots + A_4 2^{-4}$$

$$A = (1 - A_0) 2^0 + \dots + (1 - A_4) 2^{-4}$$

$$A + \overline{A} = 2^0 + \dots + 2^{-4} = 2 = 2^{-4}$$

$$A = \overline{A} + 2^{-4} = 2$$

$$B = A = B + \overline{A} + 2^{-4} = 2$$

We can now construct a table which describes the operation of the i<sup>th</sup> stage of our subtractor; it is the ordinary table for binary addition where the second term is  $A_1$  instead of its complement,  $A_i$ . Note that we require an "instantaneous" carry output,  $K_{i=1}$ .

| B <sub>1</sub> (t) | Ag (t)      | K <sub>i</sub> (t) | <b>x</b> <sub>1-1</sub> (t) | $B_{\underline{1}}(t+T)$ |

|--------------------|-------------|--------------------|-----------------------------|--------------------------|

| 0                  | 0           | 0                  | 0                           | 0                        |

| 0                  | 0           | 1                  | 0                           | 1                        |

| 0                  | 1           | . 0                | 0                           | 1                        |

| 0                  | 1           | 1                  | 1                           | 0                        |

| 1                  | 0           | 0                  | 0                           | 1                        |

| 1                  | 0           | 1                  | 1                           | 0                        |

| 1                  | 1           | 0                  | 1                           | 0                        |

| 1                  | 1           | 1                  | 1                           | 1 ;                      |

|                    |             |                    |                             |                          |

| all pos            | sible imput |                    | B +                         | Ä                        |

We want in the B-register at time t+T not  $B+\overline{A}$ , but rather  $B+\overline{A}+2^{-4}-2$ , which we have shown above to be equal to B=A. (cf. end-around carry)

To get from  $B+\overline{A}$  to  $B+\overline{A}+2^{-4}-2$ : we add the  $2^{-4}$  by requiring that  $K_4$ , the carry input to the first stage, be 1.

We subtract the 2 by failing to provide a B.1 flip-flop.

Then a realization of the table which has the two additional preparties just listed will subtract the contents of A from the contents of B and leave the result in the B-register T seconds after the subtract command pulse,  $P_6E$  (note that according to the table on p.5 the  $(B) - (A) \Rightarrow B$  command goes out when the F-counter is in the configuration 110  $(P_6)$  and a clock pulse (E) occurs).

The input to  $B_1$  is to be pulsed whenever we wish  $B_1(t+T)$  to be the complement of  $B_1(t)$  and a <u>subtract</u> command pulse occurs. Comparing the first and last columns of the table we get

$$b = (B_{1}^{0}A_{1}K_{1} + B_{1}^{0}A_{1}^{0}K_{1}^{0} + B_{1}A_{1}^{0}K_{1} + B_{1}A_{1}^{0}K_{1}^{0})P_{6}$$

If this seems wrong, notice that the table lists values of  $A^{\dagger}$ , not values of A, and that  $A_{1}^{\dagger}=0$  means:  $A_{4}=1$ .

This expression can be greatly simplified by factoring  $A_1K_1$  from the first and third terms, and  $A_1K_1$  from the other two:

$$b = (A_1 K_1 + A_1^0 K_1^0) P_6 E = (A_1^0 \oplus K_1) P_6 E$$

(1 = 0, ...,4)

which fact might have been seen directly from the table.

The carry output from this stage is

$$K_{i-1} = (B_{i}^{0} \underline{A}_{i}^{0} K_{i} + B_{i} \underline{A}_{i}^{0} K_{i} + B_{i} \underline{A}_{i}^{0} K_{i}^{0} + B_{i} \underline{A}_{i}^{0} K_{i}^{0}) P_{6} \mathbf{E}$$

$$K_{i-1} = A_{i}^{0} K_{i} + B_{i} (A_{i}^{0} \oplus K) P_{6} \mathbf{E}$$

$$= A_{i}^{0} K_{i} P_{6} \mathbf{E} + B_{i} b$$

$$i = 1, 2, 3, 4; K_{4} = 1$$

#### 3.32 Shifting

The B-register is used in shifting as well as subtracting. Then before we adopt the above equation for the input to the B-register we must add terms which take account of the additional inputs required for shifting.

Referring to the diagram on p. 5 we see that the function (B)  $\Rightarrow$  B, which occurs in configuration 110 of the F-counter, is not the only one that involves B.

In configuration Oll  $(P_3)$  of the F-counter two other functions are performed: (B)  $\Rightarrow$ M[C] and  $(B_1) \Rightarrow$   $B_1$ , it being understood that the number which appears in M[C] is (B) before the shift. (See remarks on "simultaneous" interchanges between registers in Section 2.1.) In the shift a zero is introduced in the left-most digit position,  $B_0$ .

The transfer to memory, (B)  $\Rightarrow$  M[C], does not concern the <u>input</u> to the B-register: it will be taken account of in the input equations to memory. Then the input equations for b will be complete when we add expressions to realize (B<sub>i</sub>)  $\Rightarrow$  B<sub>i+1</sub>(i = 0,1,2,3); 0  $\Rightarrow$  B<sub>0</sub>. This is most easily done using the <u>clear</u> and <u>set</u> inputs to the B flip-flops, although it might have been accomplished with only the complement input, with suitable gating. Then we consider that we have the WWI type of FF with three inputs, labeled as shown; the complete equations for the B-register are then

$$b_{i} = (A_{i}^{0} \oplus K_{i})P_{6}E \qquad (i = 0,1,2,3,4) \quad (difference \ digit)$$

$$K_{i-1} = A_{i}^{0}K_{i}P_{6}E + B_{i}b \quad (i = 1,2,3,4) \quad (carry)$$

$$K_{4} = 1 \quad (mend-around \ carry^{n})$$

$$1^{b_{1}} = B_{i-1}P_{3}E$$

$$0^{b_{1}} = B_{i-1}P_{3}E$$

$$0^{b_{2}} \quad (destructive \ shift)$$

That is, when the F-counter is in configuration P3, the clock pulse E acts as a command for the contents of register no. i-1 to appear in register no. i, and for a zero to appear in register  $B_0$ . It is assumed, once again, that there is a delay inherent in the inputs to our FF's such that this shifting will occur after the transfer to memory has taken place.

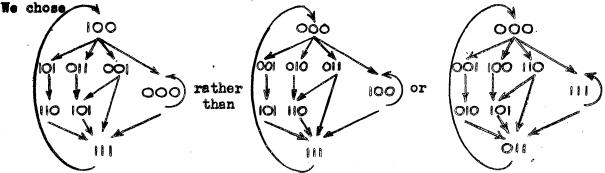

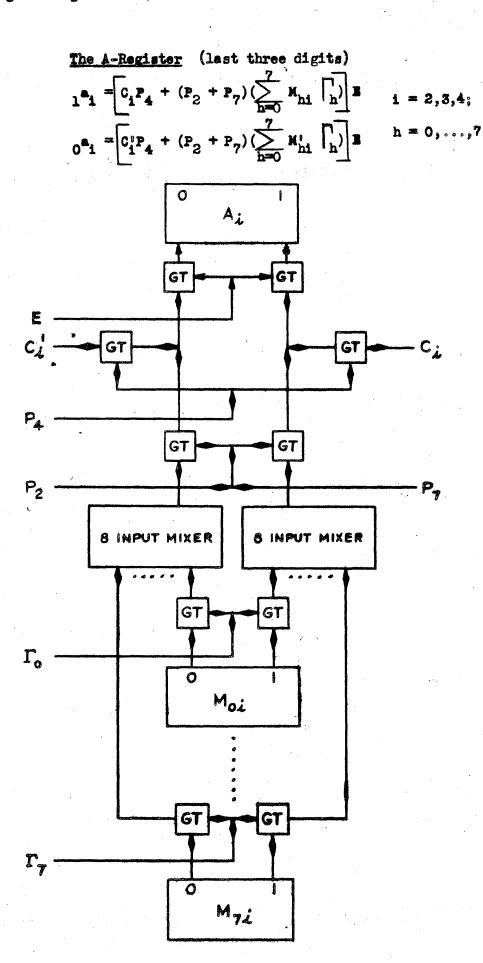

# 3.33 The A-Register (See diagram, p. 25)

To complete the discussion of the arithmetic element we write the equations of the inputs to the A-register. Transfers into A occur on configurations 100, 010, and 111 (P<sub>4</sub>, P<sub>2</sub> and P<sub>7</sub>) of the operation counter (see p. 5). Again it will be simplest to use the <u>set</u> and <u>clear</u> inputs rather than the <u>complement</u> input:

an the complement input:

$$\mathbf{1}^{\mathbf{a}_{1}} = \begin{bmatrix} \mathbf{c}_{1} \mathbf{P}_{4} + \mathbf{M}_{hi} (\mathbf{P}_{2} + \mathbf{P}_{7}) \\ \mathbf{0}^{\mathbf{a}_{1}} = \begin{bmatrix} \mathbf{c}_{1}^{0} \mathbf{P}_{4} + \mathbf{M}_{hi}^{0} (\mathbf{P}_{2} + \mathbf{P}_{7}) \\ \mathbf{1}^{\mathbf{a}_{1}} = \mathbf{M}_{hi} (\mathbf{P}_{2} + \mathbf{P}_{7}) \\ \mathbf{0}^{\mathbf{a}_{1}} = \mathbf{M}_{hi}^{0} (\mathbf{P}_{2} + \mathbf{P}_{7}) \end{bmatrix}$$

$$\mathbf{1} = 2, 3, 4$$

It is necessary to treat i = 0, l separately since there are no  $C_0$  or  $C_1$  flip-flops. Now we must explicitly indicate how h = (C) is to be implemented.

Let us assign names to the configurations of the C-register in analogy to the P<sub>1</sub> as names for the configurations of the F-register:

Now the C-register will be in one and only one of these configurations at any time and hence for any fixed i

$$\begin{bmatrix}

c_1^2 c_2^2 c_3^2 c_4 \\

c_2^2 c_3^2 c_4

\end{bmatrix}$$

$$\begin{bmatrix}

c_2^2 c_3^2 c_4 \\

c_2^2 c_3^2 c_4

\end{bmatrix}$$

will be 0 or 1 accordingly as the ith digit of the word in memory which corresponds to (C) is 0 or 1.

This implements the condition h = (C) which we added verbally to the equation above.

Then the final equations for the A-register are

$$1^{a_1} = \begin{bmatrix} c_1 P_4 + (P_2 + P_7) & h_1 & h_2 \\ b_1 & h_2 & h_1 & h_2 \end{bmatrix}$$

$$0^{a_1} = \begin{bmatrix} c_1 P_4 + (P_2 + P_7) & h_1 & h_2 \\ c_1 P_4 + (P_2 + P_7) & h_1 & h_2 \end{bmatrix}$$

$$1 = 2_y 2_y 4$$

$$1^{a_1} = (P_2 + P_7) & h_1 & h_2 \\ 0^{a_1} = (P_2 + P_7) & h_1 & h_2 \end{bmatrix}$$

$$1 = 0,1$$

### 3.34 The C-Register

The inputs to the C-register are affected in configurations 100, 010, 011, 001 (in case  $B_0 = 0$ ) and 101 of the operation counter, and in case G = 0, regardless of the state of F (see p. 5). Only three different things go on:

(1) (Ad A) = C (on

$$P_A$$

,  $P_2$ ,  $P_3$  and  $P_1B_0$ )

(2)

$$0 = C \text{ (on } G^{0})$$

(3) (C) + 1 = C (en

$$P_5$$

)

The first two functions are easily handled as above, using the set and clear imputs:

$$\begin{vmatrix}

1^{a_1} = (P_1 B_0^1 + P_2 + P_3 + P_4) A_1 B \\

0^{a_1} = ((P_1 B_0^1 + P_2 + P_3 + P_4) A_1^2 + 6^{\frac{1}{2}} B

\end{vmatrix} 1 = 3, 3, 4$$

The "G'" term in the equation for Oci provides that when the computer is started up, the first memory address to be referred to will be 000.

The <u>edd one</u> function can be implemented by a simple counter using the <u>complement</u> imputs. The cycle for the counter is:

Apparently the stages should be complemented as follows:

### 3.35 The Start Flip-Flop, G

On the halt command, on the time pulse before the operation (F) counter reaches configuration 000 the G flip-flop is cleared and therefore the F-counter sticks on 000 (see p. 5). The machine is to be started again by use of a switch, S, which sets G and allows the next clock pulse to step the operation counter into configuration 111. The machine can be stopped not only on the halt command, but at any time by setting S to off.

$$O^{\mathcal{E}} = (P_4 A_0^{\dagger} A_1^{\dagger} + S^{\dagger}) \mathbf{E}$$

$$O^{\mathcal{E}}$$

$$O^{\mathcal{E}}$$

$$O^{\mathcal{E}}$$

$$O^{\mathcal{E}}$$

Shown in rest position. Can be lecked in off. Centact in on state is momentary.

# 3.36 The Memory

Read-in to the memory is to be accomplished in one of two ways

- (1) Program: in the Oll configuration of the operation counter (B)  $\Rightarrow$  M[C].

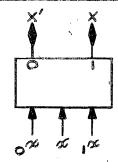

- (2) Fill Buttons: the individual flip-flops can be filled "by hand"; this method is used for reading in programs.

The "fill buttons" are switches which in their rest positions excite meither on nor on.

$$\begin{bmatrix} \mathbf{1}^{\mathbf{w}_{\mathbf{d}}} = (\mathbf{R}_{\mathbf{w}_{\mathbf{d}}} + \mathbf{B}_{\mathbf{d}} & \mathbf{P}_{\mathbf{3}}) \mathbf{E} \\ \mathbf{0}^{\mathbf{w}_{\mathbf{d}}} = (\mathbf{R}_{\mathbf{w}_{\mathbf{d}}}^{0} + \mathbf{B}_{\mathbf{d}}^{0} & \mathbf{P}_{\mathbf{3}}) \mathbf{E} \end{bmatrix} \quad \mathbf{w} = 0, \dots, 7 \quad \text{Fill Button}$$

$$\mathbf{d} = 0, \dots, 5 \quad \mathbf{R}_{\mathbf{0}}^{0} \quad \mathbf{A} \quad \mathbf{0}^{\mathbf{R}}$$

$$\mathbf{Read in} \quad \mathbf{Read in} \quad \mathbf{Read$$

Shown in rest position. Contact is momentary in both positions.

We now have a set of equations which completely describe the logic of our machine. They are summarized on p. 21 and p. 22.

#### 4.0 GENERAL REMARKS

There are three general stages in the development of the logic of any particular computing machine. In order of decreasing generality of the decisions involved, they are:

- (1) <u>Planning</u>. (Given the purpose of the machine, what operations shall be included? What word-length? What speed per operation?....)

- (2) <u>Combinatorial Decisions</u>. (What general arrangement of devices will best implement the <u>plan</u>: what shall be the cycle of the operation counter? What order code? What basic functions (commands)?....)

- (3) <u>Design</u>. (What configuration of memory-elements, gates, mixers, etc. best realizes the results of the combinatorial decisions?)

In the case of the present "sample" computer these steps went somewhat as follows:

- (1) Planning: The purpose of the machine was to serve as an example of a method of design. Therefore it should have a small memory, short word length and few operations; but none of these should be so short, small or few as to make the design problem trivial. The results of the planning were presented, without discussion, on the first three pages.

- (2) <u>Combinatorial Decisions</u>: These are summarized by the table on p. 5. There the cycle of the operation-counter is shown and the groups of basic commands indicated. Since the operations are few and simple, no thought at all was devoted to the coding of them (00 =halt, 01 = <u>cp</u>, etc.)

- (3) <u>Design</u>: Throughout the design we referred to the table on p. 5 which summarized the combinatorial decisions. The design is almost mechanical, once the table has been drawn.

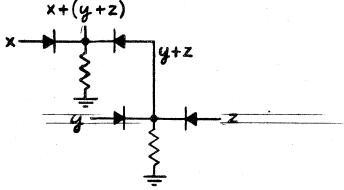

The sort of problem involved in the combinatorial decisions is illustrated by the binary coding of the 8 boxes in the lattice on p. 5.

because we thought that of all the 8! ways of assigning numbers from 0 through 7 to the 8 points in the lattice, the one selected resulted in the simplest design. Of course we did not draw up all 8! lattices and from them write 8! sets of equations for the machine, examine them and choose the one that contained the fewest components. Such a program might be carried out by a machine like WWI, but not by human beings. Rather we considered e.g. that it would be desirable to have as little difference as possible between the numbers assigned to the points in the second level of the diagram, the outcomes of the four-way choice after 100. Accordingly, in a simple-minded way, we decided to use the four numbers beginning with "O" for those points. Similarly in the binary decision after 001 we chose "101" and "111" as the numbers of the next configurations because they differ from each other only in a single digit.

To systematize such combinatorial decisions, three developments would be helpful:

- (1) A mathematical theory of the desirability of such choices as the two mentioned above (which were made on an intuitive basis).

- (2) Assignment of numerical values to different components and their configurations (the unit might be dollars, or speed, reliability or some combination of those). Any such assignment should be in general terms so that the parameters might be changed as the characteristics of available components change.

- (3) Programs which would allow a high-speed computer to survey large numbers of possibilities such as the 8% assignments of numbers to the points in the lattice above. It is possible to write down a fully mechanical procedure for simplifying equations and even for going from a diagram like the one on p. 5 to a set of equations, so that this development is possible and perhaps practical.

#### 5.0 SUMMARY

#### 5.1 Complete Set of Equations for the Machine

# 5.11 Abbreviations

$P_1 = F_1^*F_2^*F_3^*$  where the  $n^{th}$  max is either a prime or a blank, depending on whether the  $n^{th}$  digit in the binary representation of i is a "O" or a "1". e.g.,  $P_5 = P_{101} = F_1F_2^*F_3$ .

$$\sum_{i=1}^{n} \mathbf{x}_{i} = \mathbf{x}_{1} + \mathbf{x}_{2} + \dots + \mathbf{x}_{n}$$

### 5.12 Notation for Flip-Flops

# 5.13 The Operation Counter (F-Register)

$$f_1 = (P_0G + P_1 + P_2 + P_3 + P_4)E$$

$f_2 = (P_0G + P_1B_0 + P_3 + P_4A_0 + P_5 + P_7)E$

$$f_3 = (P_0G + P_4A_1 + P_6 + P_7)E$$

$$0^{f_i} = 0^{\circ}E \quad (i = 1, 2, 3)$$

#### 5.14 The Accumulator (B-Register)

$$b_i = (A_i^1 \oplus K_i)P_6E \quad (i = 0,1,2,3,4)$$

$$\begin{bmatrix}

1^{b_1} &= B_{1-1}P_3E \\

0^{b_1} &= B_{1-1}^{0}P_3E

\end{bmatrix}$$

(1 = 1,2,3,4)

$$0^{b_0} = P_3^{E}$$

$$\mathbf{K_{i-1}} = \mathbf{A_i^1 K_i P_6 B} + \mathbf{B_i b} \quad (i = 1, 2, 3, 4); \quad \mathbf{K_4} = 1$$

5.15 The A-Register

$$1^{a_{1}} = \begin{bmatrix} c_{1}P_{4} + (P_{2} + P_{7}) & 7 \\ h=0 \end{bmatrix} \times \begin{bmatrix} 7 \\ h=0 \end{bmatrix} \times \begin{bmatrix} 1 \\ h \end{bmatrix} = \begin{bmatrix} 1 \\ 1 \end{bmatrix} \times \begin{bmatrix} 1 \end{bmatrix} \times \begin{bmatrix} 1 \\ 1 \end{bmatrix} \times \begin{bmatrix} 1 \\ 1 \end{bmatrix} \times \begin{bmatrix}$$

Same for i = 0,1 except that lst term is missing.

# 5.16 The Memory-Selection Register (C)

$$\begin{vmatrix}

\mathbf{c_i} &= \mathbf{X} \mathbf{A_i} \mathbf{E} \\

\mathbf{c_i} &= (\mathbf{X} \mathbf{A_i}^{0} + \mathbf{G}^{0}) \mathbf{E}

\end{vmatrix} \qquad i = 2, 3, 4$$

where

$$X = P_1 B_0^0 + P_2 + P_3 + P_4$$

.

$$c_i = C_{i+1}$$

(i = 2,3)

$$c_4 = P_5 \mathbf{E}$$

# 5.17 The Start-Stop Flip-Flop (G)

$$_{0}$$

g =  $(P_{4}A_{0}^{0}A_{1}^{0} + S^{0})E$

S is a double-throw switch which can be locked in the off position, makes momentary contact in the on position, and has a rest position in which neither contact is energized.

# 5.18 The Memory Registers (M)

The R<sup>1</sup>s are double-throw switches ("fill buttons") which make momentary contact on either side and have a rest position in which both sides are open.

(Read in 0) (Read in 1)

Shown in rest position

#### 5.2 The Flip-Flops

These are assumed to have an inherent delay between receipt of an input pulse and the resulting change in the output. Speaking loosely, this delay permits reading new information into a register "at the same time" that the old information is being read out, and permits "simultaneous" transfers of information between two registers. (See Section 2.1.)

#### 5.3 Operating Instructions

- 1. Turn on power and allow tubes to warm up. During this time the machine will be cycling through some meaningless program if the G flip-flop happens to start out holding a "l".

- 2. Lock switch S in the off position. This sets G to O, sets the operation counter to 000, and reads 000 into C. Read program and data into memory with "push-buttons" (R).

- 3. Release S (mothing happens while S is in neutral position), push it to the on position and release. This sets G to 1 and the operation counter steps into 111, the beginning of program timing. Since C holds 000, the first word to be taken out of memory and transferred into the A-register will come from the first memory register (at location 000). The program should be stored with this fact in mind.

- 4. The program should end with a halt command, 00xyz, where x y z may be any number. This freezes the contents of all FF's except for G and the F and C registers, all of which are cleared. A new program may now be read into storage via the R switches and the machine may be re-started by pushing the S switch over to on.

- 5. Read-out is via meon bulbs attached to the memory FF s (not shown above).

#### 5.4 Block Diagrams

People who are unfamiliar with the algebraic netation may find it helpful to translate some of the equations into block diagrams. A little bit of this will go a long way toward promoting familiarity with the algebraic symbolism; with a little practice it will be found that as much information can be read directly from a few lines of equations as from a dense page of block diagrams.

Block diagrams for a few of the registers follow.

Note that the equations for a register show the <u>inputs</u> to that register. To find <u>cutputs</u> of register X, look through all the equations for occurrences of the letter "X". (In the case of the F and C registers, look for "P" and "P" as well, since these abbreviate products of "F" s and "C"s.)

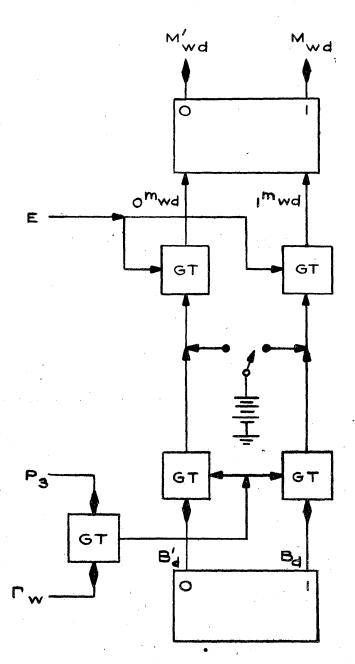

Memory

$$1^{m} w d = (R_{wd} + B_{d} | W P_{3}) E$$

$$0^{m} w d = (R_{wd}^{0} + B_{d}^{0} | W P_{3}) E$$

$$d = 0, ..., 5$$

Identical picture for each memory cell.

In case a magnetic core memory is used with an I/2 selection system, the read-in gates are simply points where pairs of insulated wires cross inside the cores.

This memory system is not intended as a prac tical proposal. The following two modifications are desirables (1) In reading out of memory, clear A on the preceding clock pulse and then read into onl the set sides of the A FF's. This climinates the left hand half of the memory read-out gates and the left han 8 input mixer. (2) Use magnetic cores as memory cells. Then th remaining read-out gates are inherent in the cores, and the S input mixer is the sensing winding.

# The Accumulator (complement inputs)

The <u>set</u> and <u>clear</u> inputs are used only for shifting. The reader can complete this diagram by adding them.

$$b_i = (A_i^* \bigoplus K_i)P_6 E \quad (i = 0, ..., 4)$$

$$K_{i-1} = A_i^* K_i P_6 E + B_i b$$

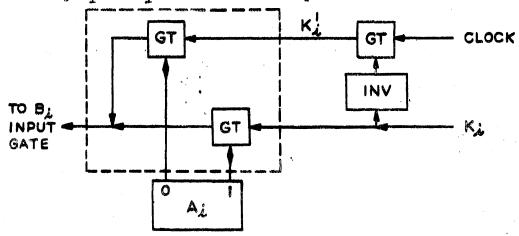

represents a black box which gives a pulse output whenever one but not both of the inputs are present. See next page.

The black box for partial sum ( $\oplus$ ) is an eversimplification. Probably the best way to implement it with customary electronic components is to use not only  $\mathbb{A}_1$  and  $\mathbb{K}_1$  but also their complements:

This requires either providing an inverter to get  $K_1^i$  out of  $K_4$ , or building up  $K_{1-1}^i$  as an output from stage #i independent of  $K_4$ . (A carry zero line as well as a carry one line.)

Richard C. Jeffrey

Irving & Road

APPROVED N. H. Taylor

# RCJ/ISR/cp

CC: G. R. Briggs R. P. Mayer

D. R. Brown J. A. O'Brien

D. A. Buck W. Ogden

H.R.J. Grosch K. H. Olsen

W. A. Hosier W. N. Papian

J. Jacobs W. Linvill

### **BIBLIOGRAPHY**

- 1. Jeffrey, R. C., Reed, I. S., "The Use of Boolean Algebra in Logical Design", Engineering Note E-458-1, Digital Computer Laboratory, M.I.T., (April, 1952).

- 2. Reed, I. S., Division II Status Report, Project Lincoln, (April, 1952).

- 3. Reed, I. S., "Some Mathematical Remarks on the Boolean Machine", Project Lincoln Technical Report No. 2, (December 19, 1951).